COT控制模式简述Part10——TI的DCAP控制器

作者:Evan 远远,魔都漂流的孤独患者。

热爱电力电子和模拟电路,希望大家一起交流。

众所周知,德州仪器一直以来就是排名第一的模拟大厂,其电源控制器和模拟信号链产品占据较大的份额。

因此,非常有必要说一说 TI 的 DCAP 系列控制器,它被广泛地应用在计算机、服务器以及存储等领域。

前面已经说过 DCAP 控制器也是 ACOT 原理的控制器,TI 把它称为“Direct connection to the output CAPacitor”,缩写为 DCAP。

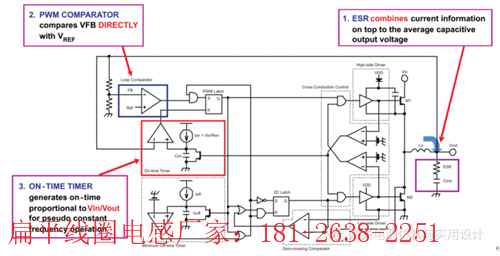

图 42DCAP 控制器框图相信看过 TI 官网资料的朋友一定对这个 DCAP 控制器框图很熟悉。

图 42DCAP 控制器框图相信看过 TI 官网资料的朋友一定对这个 DCAP 控制器框图很熟悉。

它和我们之前搭建的 COT 控制器的模型基本一致,包含了恒定时间定时器(On-time Timer)、最小关断时间定时器(Minimum Off-time Timer)、电流过零检测(Zero-crossingDetection)、以及上下管的驱动。

输出电压通过简单的分压网络做采样得到含有 ESR 纹波的反馈信号,反馈信号 vfb 和参考电压 vref 比较,当 vfb 低于 vref 时,比较器输出拉高。

此时,最小关断定时器也需要准备好,在上一个开关周期中关断阶段,当 PWM latch Q 拉低时,最小关断定时器才开始以恒定电流 Ioff 给 Coff 充电,当 Coff 电压大于设定好的参考电压时,最小关断定时器的比较器输出一定会拉高。

接着往右看,这里多了一个或门,PWM latch Q 是拉低的,最小关断定时器的输出是拉高的,因此或门的输出在上一个周期的关断阶段一定是高电平。

这个高电平输入到与门,它会一直等待 vfb 低于 vref,Loop 比较器拉高信号的到来。

等与门的两个输入都为高电平之后,PWM latch 的 S 拉高,使得 PWMlatch Q 拉高,从而驱动上管的驱动拉高。

只不过在这里,PWM latch Q 的高电平信号之后接入了另一个与门,它也需要等待下管关断信号结束,防止上下管的直通,也即是图中的 cross conduction control。

同样地,下管的驱动信号做了一毛一样的逻辑处理。

恒定导通定时器的控制和之前表述的 ACOT 一毛一样,不多言。

值得注意的是,ZCD 过零检测部分,与之前介绍的方式比较类似。

通过在关断阶段采样开关结点的电压,当电压逐渐增大变为正电压时,比较器翻转,关断下管的驱动信号,从而进入 DCM 模式。

想象一下,ZC latch 的 S 端什么时候会拉高呢?S 端接入了一个非门,在非门之前的信号就是最小关断定时器的输出和 PWM latch Q 输出的或信号。

所以,只有一种,PWM latch Q 和最小关断定时器的比较器输出,两者都拉低。

实际上,PWM latch Q 控制着最小关断定时器 Coff 电容电压。

Q 拉高,Coff 电压被放电至零,最小关断定时器的比较器输出一定是低;Q 拉低,Coff 电压被充电,未充到设定的参考电压时,最小关断定时器的比较器输出是低,充到设定的参考电压时,最小关断定时器的比较器输出为高。

所以,只有在最小关断定时器充电阶段,才满足上述两者均拉低的要求。

因此可以判定,ZC latch S 由 Q 拉低触发,这么做当然是为了 SW 降低到二极管钳位电压之后才开始采样。

笔者比较担心的是,从 Q 信号到 SW 真正拉低至下管的体二极管钳位电压时,仍然有比较大的时间延迟。

就有可能出现,Q 拉低触发 ZCD 检测开始,而 SW 还处在从 Vin 下降的阶段,从而引起 ZCD 信号误动作。

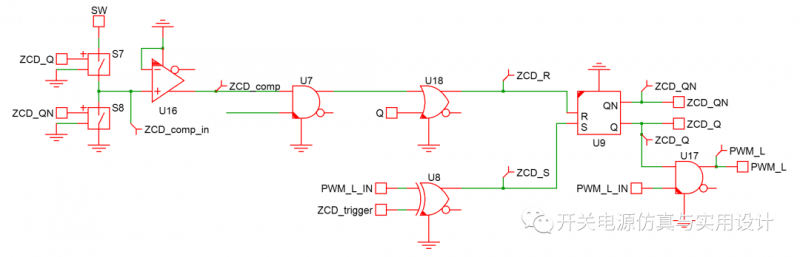

图 43 part9 中的 ZCD 逻辑(为了方便表述,再贴一次)细心的读者会发现,(如果跑过我分享的仿真模型)在上一篇的文章图中,ZCD latch S 的触发信号,使用了一个比较投机取巧的方法。

图 43 part9 中的 ZCD 逻辑(为了方便表述,再贴一次)细心的读者会发现,(如果跑过我分享的仿真模型)在上一篇的文章图中,ZCD latch S 的触发信号,使用了一个比较投机取巧的方法。

上下管驱动一定是需要死区时间的。

将下管的 PWM 信号在 delay 一定的时间获得 ZCDTrigger 信号,将两者异或,就可以获得一个从下管 PWM 开始的脉冲信号。

这样做的好处是,下管 PWM 开始时刻,足够保证 SW 电压已经降低到负的二极管钳位电压。

再回头来看 DCAP 框图,ZCD latch Q 拉高,将 SW 接入 过零比较器 Zero-crossing Comparator 与 GND 比较。

当 SW 电压大于 GND 时,说明电感电流已经过零了,此时需要关断下管的 PWM 信号。

而下管的 PWM 信号与 ZCD latchQ 信号是相与关系,因此只要拉低 ZCD latch Q 即可,也即置位 ZCD latch R 端。

当电感电流过零时,过零比较器的输出与 PWM latch Q 信号相或,此时 PWM latch Q 信号一定是低电平,则它俩的或门输出为高电平,或门之后接了一个与门。

与门的另一端是最小关断定时器的比较器输出与 PWM latch Q 相或后的信号,根据之前的分析,只有 Coff 电容充电阶段,最小关断定时器的比较器输出与 PWM latch Q 相或后的信号才为低电平,其他时刻均为高电平。

所以,与门的输出信号,在 Coff 电容充电结束以及过零比较器输出拉高时,一定为高电平,从而置位 ZCD latchR 端,顺利地关闭下管的 PWM 信号。

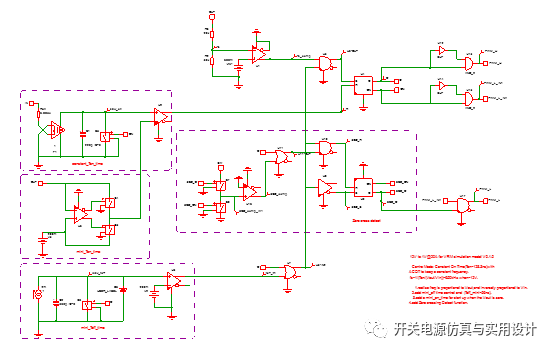

图 44 simplisDCAP 仿真在 Simplis 仿真方面,基本控制框图类似,ZCD 检测基本和 DCAP 控制框图保持一致,增加了 PWM 驱动死区时间。

图 44 simplisDCAP 仿真在 Simplis 仿真方面,基本控制框图类似,ZCD 检测基本和 DCAP 控制框图保持一致,增加了 PWM 驱动死区时间。

在线客服1号

在线客服1号