小课堂开课:SiC MOSFET的桥式结构探讨

2021-09-15 11:24:55 点击:

上一篇:手机无线充电从鸡肋到刚需 究竟有哪些原因

栏目ID=7的表不存在(操作类型=0)

栏目ID=8的表不存在(操作类型=0)

栏目ID=9的表不存在(操作类型=0)栏目ID=10的表不存在(操作类型=0)

在探讨“SiC MOSFET:桥式结构中 Gate-Source 电压的动作”时,本文先对 SiC MOSFET 的桥式结构和工作进行介绍,这也是这个主题的前提。

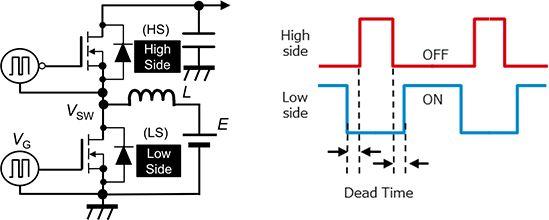

SiC SiC MOSFET 的桥式结构下面给出的电路图是在桥式结构中使用 SiC MOSFET 时最简单的同步式 boost 电路。

该电路中使用的 SiC MOSFET 的高边(HS)和低边(LS)是交替导通的,为了防止 HS 和 LS 同时导通,设置了两个 SiC MOSFET 均为 OFF 的死区时间。

右下方的波形表示其门极信号(VG)时序。

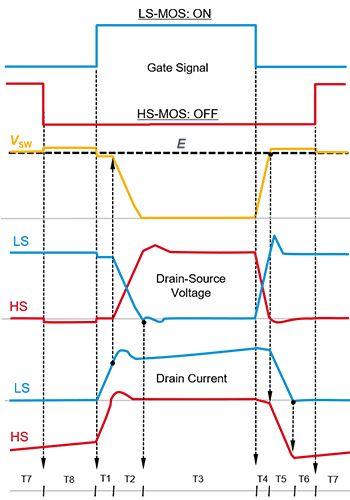

该电路中 HS 和 LS MOSFET 的 Drain-Source 电压(VDS)和漏极电流(ID)的波形示意图如下。

该电路中 HS 和 LS MOSFET 的 Drain-Source 电压(VDS)和漏极电流(ID)的波形示意图如下。

这是电感 L 的电流处于连续动作状态,即所谓的硬开关状态的波形。

横轴表示时间,时间范围 Tk(k=1~8)的定义如下:T1:LS 为 ON 时、MOSFET 电流变化的时间段T2:LS 为 ON 时、MOSFET 电压变化的时间段T3:LS 为 ON 时的时间段T4:LS 为 OFF 时、MOSFET 电压变化的时间段T5:LS 为 OFF 时、MOSFET 电流变化的时间段T4~T6:HS 变为 ON 之前的死区时间T7:HS 为 ON 的时间段(同步整流时间段)T8:HS 为 OFF 时、LS 变为 ON 之前的死区时间

横轴表示时间,时间范围 Tk(k=1~8)的定义如下:T1:LS 为 ON 时、MOSFET 电流变化的时间段T2:LS 为 ON 时、MOSFET 电压变化的时间段T3:LS 为 ON 时的时间段T4:LS 为 OFF 时、MOSFET 电压变化的时间段T5:LS 为 OFF 时、MOSFET 电流变化的时间段T4~T6:HS 变为 ON 之前的死区时间T7:HS 为 ON 的时间段(同步整流时间段)T8:HS 为 OFF 时、LS 变为 ON 之前的死区时间

在线客服1号

在线客服1号